最新上架

更多- 长晶科技CJ6388与CJ88XX系列LDO:以低功耗与高PSRR赋能稳定供电

- 风华叠层片式铁氧体大电流磁珠CBW系列为高功率应用场景提供可靠的解决方案

- 风华CMP系列叠层片式铁氧体功率电感CMP201209、CMP321609、CMP252009等系列特性与应用

- 君耀GDT气体放电管2R-4-H3.5系列与2R-4x5系列对比分析

- 风华高科插件式限流型PTC热敏电阻器的技术特点、型号规格、性能参数及应用场景

- 长晶科技 1.5A 三端稳压器产品线概览及选型指南

- 风华高科CBU系列叠层片式铁氧体超大电流磁珠特性、参数与应用指南

- 高可靠性过流保护解决方案--君耀电子BK16系列PPTC产品深度解析

- 风华高压温度补偿型陶瓷电容器CC81系列是液晶显示等领域的理想元件

- 20KPA 系列 TVS 二极管:高功率瞬态过压防护之选-国巨君耀代理商

上海贝岭新品BL1065/BL1066系列:8通道、16位、125MSPS模数转换器

上海贝岭最新推出的BL1065/BL1066系列是一组8通道、16位、最高125MSPS、串行LVDS数据接口的模数转换器。分别包含80MSPS、125MSPS两种速度等级以及16位、14位两种分辨率规格。采用模拟1.8V供电、数字1.8V供电,支持最大2Vpp模拟信号输入,采样时钟支持LVPECL/CMOS/LVDS电平标准输入。正常工作时功耗为1058mW。

其内置1V的高精度电压基准源,无须外部提供即可满足多种应用需求。内置PLL将自动倍频采样时钟,从而保证LVDS串行数据正确输出,最大可支持1Gbps/Lane。BL1065/BL1066系列包含2个Bank,每一个ADC Bank提供一个数据时钟输出(DCO),用于在输出端捕获数据;以及一个帧时钟输出(FCO),用于发送新输出字节信号。

BL1065采用144引脚 BGA封装,封装引脚兼容 ADI的 AD9681产品,额定温度范围为-55℃至+125°C;BL1066采用140引脚BGA封装,封装引脚兼容ADI的LTM9011-14产品,额定温度范围为−55°C至+125°C。

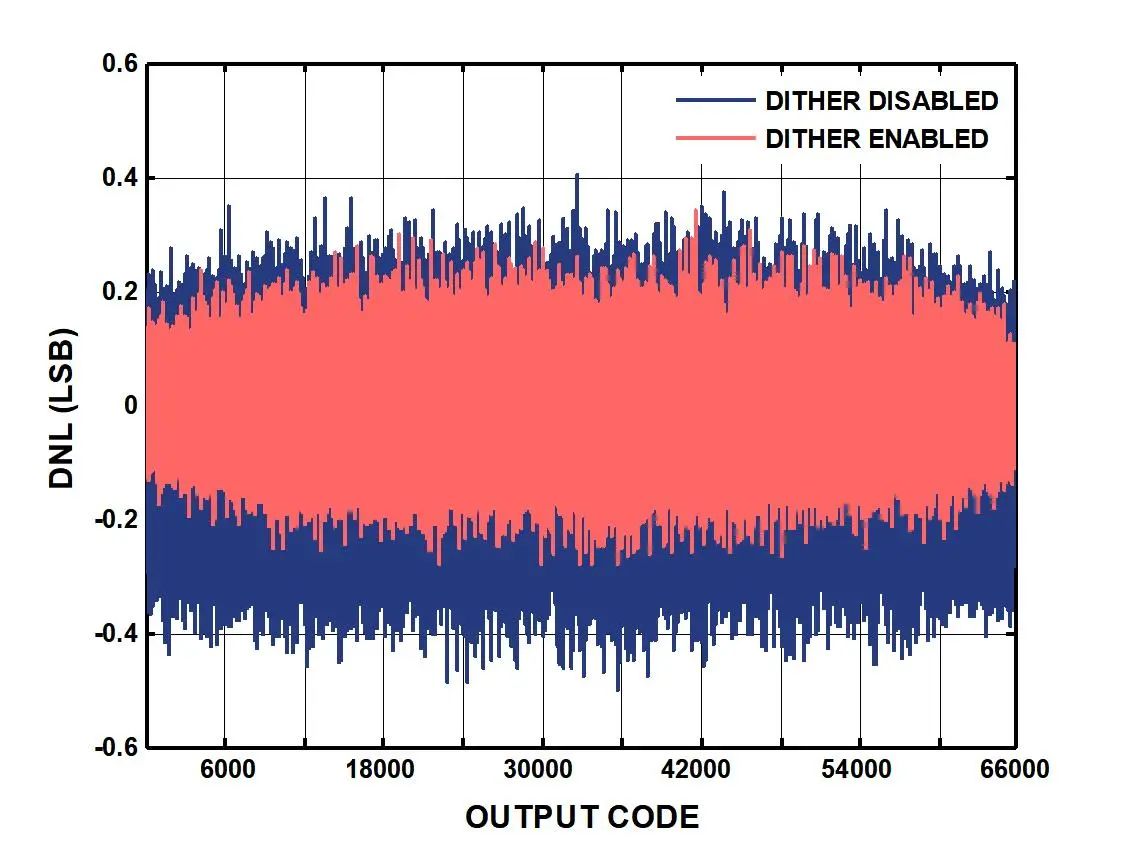

BL1065/BL1066系列产品内置dither功能,具有极佳的小信号线性度。产品可广泛应用于雷达、医疗成像系统、多通道数据采集系统、通讯系统接收机等领域。高度集成化的设计可以极大程度减小PCB设计尺寸,降低小型化设备电路布局布线难度,满足对应用系统小型化、成本最优的方案需求。

产品规格:

| 产品名 | 分辨率(位) | 采样速率(Msps) | 封装 | 相似产品 |

| BL1065-80 | 16 | 80 | BGA-144 | AD9681 |

| BL1065-125 | 16 | 125 | ||

| BL1045-80 | 14 | 80 | ||

| BL1045-125 | 14 | 125 | ||

| BL1066-80 | 16 | 80 | BGA-140 | LTM9011-14 |

| BL1066-125 | 16 | 125 | ||

| BL1046-80 | 14 | 80 | ||

| BL1046-125 | 14 | 125 |

相似产品比较:

| 参数 | BL1065/BL1066 | BL1045/BL1046 | LTM9011-14 | AD9681 |

| 通道数 | 8 | 8 | 8 | 8 |

| 分辨率 (位) | 16 | 14 | 14 | 14 |

| SNR (dBFS) | 78.9 | 77.4 | 73.1 | 74 |

| SFDR (dBc) | 92 | 89 | 88 | 90 |

| DNL (LSB) | ±0.5 | ±0.25 | ±0.3 | ±0.8 |

| INL (LSB) | ±4.5 | ±1 | ±1 | ±1.2 |

| Dither | YES | YES | NO | NO |

应用场景:

- 雷达

- 医疗成像系统

- 多通道数据采集系统

- 通信系统接收机

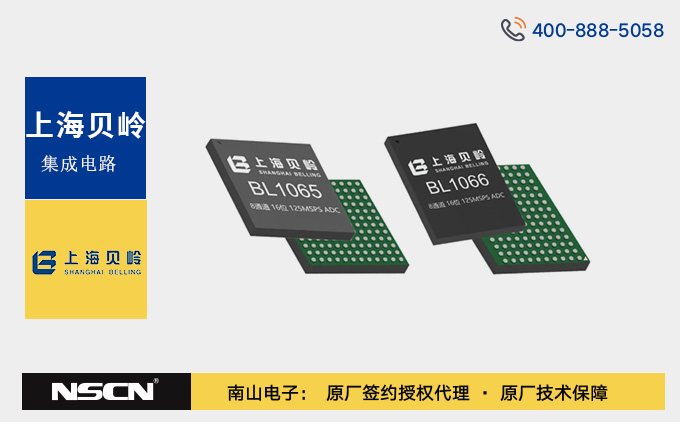

8通道125Msps ADC系统框图:

BL1065/BL1045 引脚定义(144引脚BGA):

.jpg)

BL1066BL1046 引脚定义(140引脚BGA):

-jpg.jpg)

产品特性:

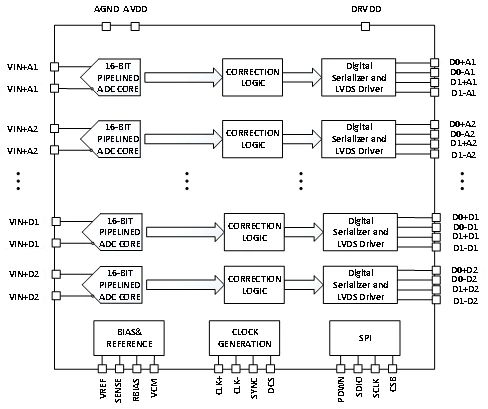

本产品具有出色的噪声性能和线性度,能够达到78.9 dBFS的高信噪比,以及±4.5 LSB 积分非线性特性。在dither开启之后,INL将进一步减小至±2.5LSB。

BL1065&BL1066 单音频谱性能(fIN=10.1MHz):

.jpg)

BL1065&BL1066 单音频谱性能(fIN=70.1MHz):

.jpg)

BL1065&BL1066 INL误差:

BL1065&BL1066 DNL误差:

高速串行LVDS接口:

ADC数据输出采用LVDS时钟同步接口,最大速率1Gbps。每路ADC两对LVDS差分输出,可选择bitwise模式(高低bit在两对LVDS差分对上交替输出,适合FPGA侧只使用 iddr原语接收)和bytewise模式(高低byte分别在两对LVDS差分对上输出,适合FPGA侧直接使用iserdes原语或selectio核接收)。

ADC数据输出接口提供多种测试码功能,用户可通过开启测试码来校准接收侧时钟和数据的相位关系,确认数据可以被正确接收。

同时我们还提供了通用的例程代码。

应用建议:

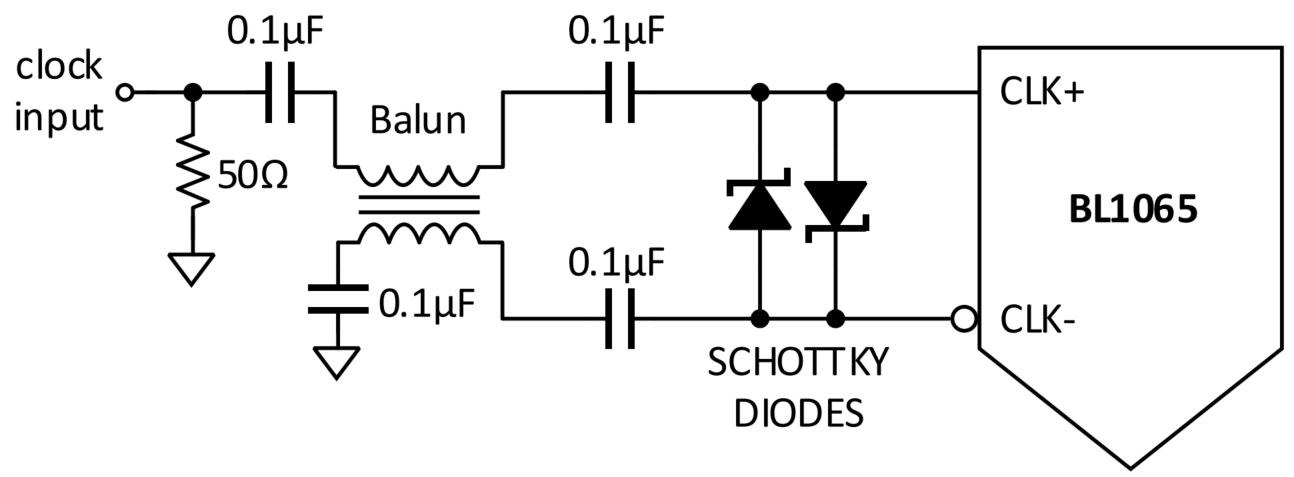

BL1065BL1066系列 典型时钟巴伦输入电路:

BL1065BL1066系列 差分双巴伦输入电路:

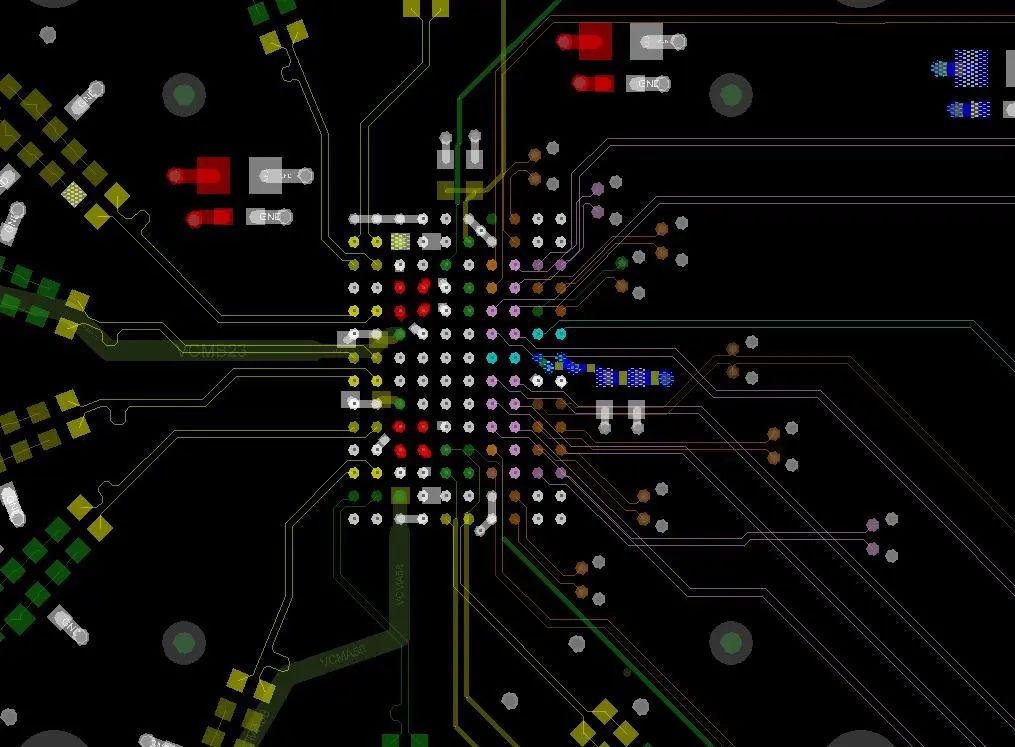

BL1066/BL1046 布局参考:

布局建议:

为了避免模拟输入之间的串扰,参考上图,并考虑以下准则:

1.布线模拟输入通道时,在PCB板的顶层和底层(或其他层)依次交替布置。

2.确保顶层通道与任何其他模拟输入通道过孔的距离不小于5mm。 3.对于底层通道,使用盘中孔以最小化通道间导体耦合对通道的影响。

4.避免平行通道的间距小于2 mm。

5.尽量将除直流通道外的走线相互正交。

本文由上海贝岭授权经销商南山电子转载自上海贝岭官方公众号,转载时内容略有修改。原文链接:https://mp.weixin.qq.com/s/i9dudeNNkyI0lTvn9_mH8w。

logo.png)